Given how important chips are to modern society EVERYONE should understand and appreciate how they are made. Every field has its own set of terms, jargon, and acronyms (engineers love acronyms!). As you would expect, chip design is no different. If you are new to chip design, it might take you a few days to read through the Wikipedia entries for each one of these 200 topics. If you are interested in actually building chips, you will need to master all 200 of them. The sources for the table can be found HERE. (PR’s appreciated)

Cheers!

Andreas Olofsson is the founder of Adapteva and the creator of the Epiphany architecture and Parallella open source computing project. Follow Andreas on Twitter.

Chip Architecture

- ADC: Analog to Digital Converter

- AES: Advanced encryption standard

- Adder: Circuit to add two numbers

- ALU: Arithmetic logic unit

- Amdahl’s Law: Amdahl’s law of diminishing returns for speeding up fixed workloads

- Arbiter: Arbitrates between competing requesters

- ASIC: Application specific integrated circuit.

- Audio codec: Device/program that compresses/decompresses digital audio

- Boolean algebra: Algebra in which variables are either true or false

- BTB: Branch target buffer

- Cache: Locally storage of program and/or data for future use.

- Cache coherence: Consistency of shared data that is stored in multiple local caches.

- CAM: Content addressable memory

- CISC: Complex instruction set computing

- Coprocessor: A processor used to supplement operations of a primary (host) processor.

- CPI: Cycles per instruction

- CPU: Central processing unit

- CRC: Cyclic redundancy check

- CSA: Carry save adder

- DAC: Digital to Analog Converter

- Distributed Computing: Computer with components working towards common goal with without strict coupling.

- DLL: Delay locked loop

- DMA: Direct memory access

- DDR Double data rate

- DDS: Direct digital synthesis

- DSM: Distributed shared memory

- DSP: Digital signal processor

- ECC: Error correcting code

- Ethernet: Family of standard network technologies

- Fault Tolerance: The ability of a system to keep operating in the event of failure of one of its components.

- FRAM: Non-volatile RAM based on ferroelectric layer.

- FPGA: Field-programmable gate array is a chip that can be reprogrammed “in the field”.

- FIFO: First in first out buffer

- GPU: Integrated circuit for accelerating the creation of graphics on a display.

- DRAM: Dynamic random-access semiconductor memory

- Flash: Non-volatile semiconductor memory

- FFT: Fast fourier transform

- FPU: Floating point unit

- GPIO: IO controllale at run time

- Gray code: Binary system where successive values differ by one bit

- HBM: High bandwidth memory

- I2C: Multi-master 2 wire bus

- LAN: Local area network

- LFSR: Linear feedback shift register

- LSB: Least significant bit

- LVDS: Low-voltage differential signaling (also TIA/EIA-644)

- MII: Media independent interface for PHY chips

- MIMD: Multiple instructionbs multiple data architecture

- MMU: Memory management unit

- MSB: Most significant bit

- MUX: Multiplexer

- Multiplier: Binary multiplier

- NCO: Numerically controlled oscillator

- NOC: Network on a chip

- Parallel Computing: A type of computation where many operations are carried out simultanesouly.

- PCM: Phase change memory

- PCIe: High Speed serial computer expansion bus

- PIC: Programmable interrupt controller

- PLL: Phase locked loop

- PWM: Pulse width modulation

- Q: Q fixed point number format

- RAID: Redundant array of disks

- Reconfigurable Computing: Collection of customizable datapaths connected together by a fabric

- RISC: Reduced instruction set computing

- ROM: Read only memory (denser than RAM)

- SBC: Single board computers

- SDR: Software defined radio

- SERDES: Serializer/deserializer

- Shift Register: Set of registars that shifts bits one position at a time

- SIMD: Single instrution multiple data

- Schmitt Trigger: Comparitor circuit wityh

- SPI: Synchronous 4 wirem aster/slave interface

- SRAM: Static random access semiconductor memory

- TLB: Translation lookaside buffer

- UART: Asynchronous 2 wire point to point interface

- USB: 2 wire point to point 5 V interface

- Video codec: Device/program that compresses/decompresses digital video

- Virtual Memory: The automatic mapping of virtual program addresses to physical addresses

- VLIW: Very long instruction level parallelism

- WAN: Wide area network

- WIFI: Wireless local area network

- 8b10b: Code that maps 8-bits to 10bit DC balanced symbols

Chip Design

- Antenna effect: Plasma induced gate oxide damage that can occur during semiconductor processing.

- Asynchronous logic: Logic not governed by a clock circuit or global clock.

- ATPG: Automatic test pattern generation

- BIST: Built in Self Test

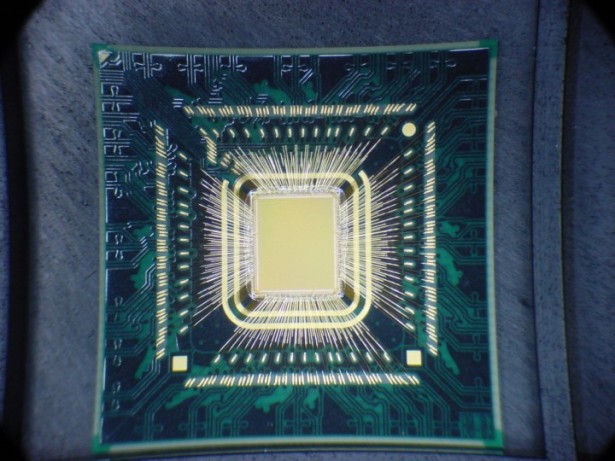

- Chip: A set of electronic circuits on one small plate (“chip”) of semiconductor material, normally silicon.

- Clock gating: Technique whereby clock in synchronous logic is shut off when idle.

- CMOS: Complimentary metal-oxide semiconductor

- Cross talk: The coupling of nearby signals on a chip, usually through capacitive coupling.

- CTS: Clock tree synthesis

- Domino logic: Fast clocked logic with reduced capacitive load

- DEF: Design Exchange Format for layout

- DFM: Extended DRC rules specifying how to make a high yielding design.

- DFT: Design for test

- Die: Small block of semiconductor material that can be cut (“diced”) from a silicon wafer.

- DRC: Design Rule Constraints specifying manufacturing constraints.

- DV: Design verification is the process of verifying that the logic design conforms to specification.

- ECO: Engineering change order

- EDA: Electronic Design Automation tools used to enhance chip design productivity.

- EDA companies: List of EDA companies

- Electromigration: Transport of material caused by the gradual movement of the ions in a conductor.

- EMI: Electromagnetic interference.

- ESD: Electrostatic discharge is the sudden flow of electricity between two electrically charged objects.

- Fabless: The design and sale of semiconductor devices while outsourcing the manufacturing to 3rd party.

- FEOL: Front end of line processing. Includes all chop processing up to but not including metal interconnect layers.

- Flip-flop: A clocked circuit that has two stable states and can be used to store state information.

- Foundry: Semiconductor company offering manufacturing services.

- Full custom design: Design methodology involving layout and interconnection of individual transistors

- GDSII: Binary format of design database sent to foundry.

- HDL: Specialized hardware description lanaguage for describing electronic circuits.

- Hold time: Minimum time synchronous input should hold steady after clock event.

- IP: Semiconductor reusable design blocks containing author’s Intellectual Property.

- IP Vendors: List of commercial semiconductor IP vendors.

- ISI: Intersymbol interference

- Jitter: Deviation from perfect periodicity.

- Latchup: Short circuit due to creation of a low-impedance path between the power supply rails of a circuit.

- Layout: Physical representation of an integrated circuit.

- LEF: Standard Cell Library Exchange Format layout.

- Logical Effort: Technique used to normalize (and optimize) digital circuits speed paths.

- LVS: Layout Versus Schematic software checks that the layout is identical to the netlist.

- Mask Works: Copyright law dedicated to 2D and 3D integrated circuit “layouts”.

- Mealy machine: A finite state machine whose outputs depend on current state and the current inputs

- MLS: Packaging and handling precautions for some semiconductors.

- Moore Machine: Finite state machine whose outputs depend only on its current state.

- Moore’s Law: Observation by Moore that the number of transistors in an IC doubles approximately every two years.

- MOSFET: Metal oxide field effect transistor.

- MOSIS: Foundry service project offering MPWs and low volume manufacturing.

- MPW: Multi-project wafer service that integrates multiple designs on one reticle (aka “shuttle”).

- MTBF: Mean time between failures

- Multi-threshold CMOS: CMOS technology with multiple transistor types with different threshold voltages.

- Optical proximity correction: Technique used to compensate for semiconductor diffraction/process effects.

- Pass Transistor Logic: Logic that connects input to non-gate terminal of mosfet transistor

- Physical design: Physical design flow (“layout”)

- PDK: Process design kits consist of a set of minimum set of files needed to design in a specific process.

- Power gating: Technique used to reduce leakage/standby power by shutting of the supply to the circuit.

- P&R: Automated Place and Route of a circuit using an EDA tool

- PVT Corners: Represents the extreme process, voltage, temperature that could occur in a given semiconductor process.

- Radiation Hardening: Act of making devices resistant to damage caused by ionizing radiation

- RTL: Design abstraction for digital circuit design

- Setup time: Minimum time synchronous input should be ready before clock event.

- SEU: Change of state caused by one single ionizing particle (ions, electrons, photons…).

- Signoff: The final approval that the design is ready to be sent to foundry for manufacturing.

- SOC: System On Chip

- Spice: Open source analog electronic circuit simulator

- STA: Method of computing the expected timing of a digital circuit without requiring full circuit simulation.

- Standard Cell Design: Design process relying on a fixed set of standard cells.

- Subthreshold Leakage: Current betwee source and drain in MOSFET when transistor is “off”.

- Synchronous logic: Logic whose state is controlled by a synchronous clock

- Synthesis: Translation of high level design description (eg Verilog) to a netlist format (eg standard cell gate level)

- SystemC: Set of C+ class and macros for simulation. Commonly used for high level modeling and testing

- Transistor: A semiconductor device used to amplify/switch electronic signals.

- Tape-out: Act of sending photomask chip database (“layout”) to the manufacturer.

- TCL: Scripting language used by most of the leading EDA chip design tools.

- Verilog: Hardware description language (HDL)

- VLSI: Very large Integrated Circuit (somewhat outdated term, everything is VLSI today)

- Von Neumann architecture: Computer architecture in which instructions and data are stored in the same memory.

Manufacturing

- BEOL: Back end of line processing for connecting together devices using metal interconnects.

- Dicing: Act of cutting up wafer into individual dies

- FinFet: Non planar, double-gate transistor.

- Photo-lithography: Process used in micro-fabrication to pattern parts of a thin film or the bulk of a substrate.

- Photomasks: Opaque plates with holes or transparencies that allow light to shine through in a defined pattern.

- Reticle: A set of photomasks used by a stepper to step and print patterns onto a silicon wafer.

- Semiconductor Fabrication: Process used to create the integrated circuits

- Silicon: Element (Si) forms the basis of the electronic revolution.

- Silicon on insulator: Layered silicon–insulator–silicon with reduced parasitic capacitance.

- Stepper: Machine that passes light through reticle onto the silicon wafer being processed.

- TSV: Vertical electrical connection (via) passing completely through a silicon wafer or die.

- Wafer: Thin slice of semiconductor material used in electronics for the fabrication of integrated circuits.

- Wafer thinning: Wafer thickness reduction to allow for stacking and high density packaging.

For More Details: 200 chip definitions everyone should know