The simple current-limiting load switch shown in Figure 1 will be familiar to most readers. In this circuit, a high level signal applied to the input switches on MOSFET Q2, which energizes the load. The load current is limited by negative feedback applied via Q1.

In most applications, the current flowing via R2 into Q1's base will be very small compared to the load current IL, so the voltage VCS developed across current-sensing resistor RCS is roughly equal to Q1's base-emitter voltage, VBE. Therefore, VBE ˜ VCS, and since VCS = ILRCS, it follows that VBE ˜ ILRCS, or IL ˜ VBE / RCS.

The value of RCS is chosen to limit the load current to a maximum value determined by IL(max) ˜ VBE(on) / RCS, where VBE(on) is the base-emitter voltage needed to bias Q1 into conduction. At room temperature, VBE(on) ˜ 650mV. So, for example, a value of RCS = 3.3O would set IL(max) to around 200mA.

Under normal, ‘no-fault' conditions, where IL is within normal limits, VBE is too small to bias Q1 on, such that MOSFET Q2 remains fully enhanced by the high level signal applied to its gate via R1. Under these conditions, the load current is determined mainly by the load resistance and the supply voltage, VS. However, if a fault causes IL to approach IL(max), Q1 starts to conduct, and reduces Q2’s gate-source voltage to a level that holds the load current roughly constant, at a value given by IL(max) ˜ VBE(on) / RCS.

This linear current limiter is very effective for applications where IL(max) and the supply voltage are not too large. However, the circuit’s ability to limit the load current safely is determined by the power dissipated in Q2. For example, if RCS is selected to set IL(max) to 400mA and if VS = 12V, a short circuit across the load would dissipate almost 5W in Q2. Not only must Q2 be capable of handling this power with adequate margin, but additional heat-sinking may be required to keep its junction temperature at a safe level. Larger values of IL(max) and/or VS would simply exacerbate this problem.

However, by adding just two inexpensive components, you can adapt the circuit to provide effective current limiting with none of the power dissipation problems. The resulting Design Idea in Figure 2 functions as a latching circuit breaker.

To understand how the circuit works, assume that INPUT is high, Q2 is on, and normal current is flowing in the load. Under these conditions, the voltage across RCS is less than VBE(on), and so Q1 has insufficient bias to conduct fully. Any slight leakage current in Q1's collector is diverted away from Q3's base via R3 which clamps the PNP's base-emitter junction voltage to a few millivolts or less, thereby holding Q3 off. Provided the load current remains within normal limits, both Q1 and Q3 remain off and have no effect on Q2.

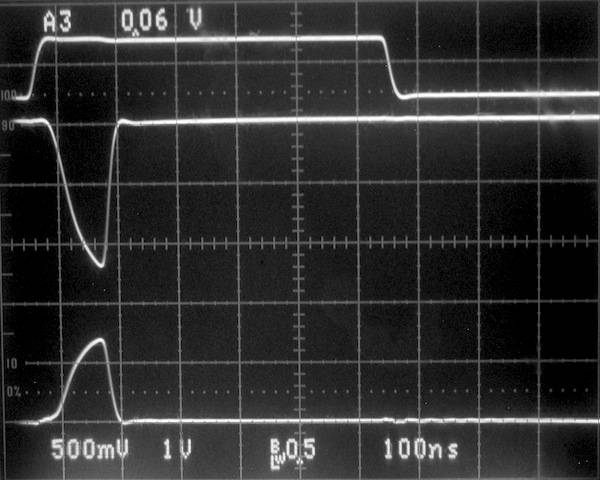

As with the simple current-limiter of Figure 1, a load fault resulting in excessive load current will increase the voltage across RCS above the 650mV needed to turn on Q1. However, additional transistor Q3 acts with Q1 to form an SCR-like structure; when Q1 turns on, it floods Q3's base with current, which itself turns on hard, sourcing more current into Q1's base. This positive feedback around Q1 and Q3 ensures that they both rapidly turn on hard.